Mạch mã hóa encoder là gì

Mạch mã hóa 4 sang 2

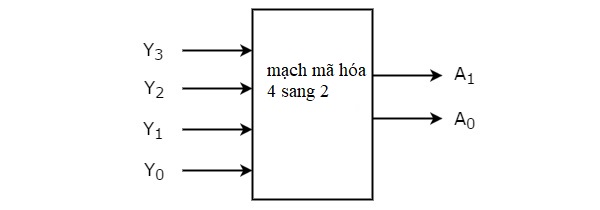

Mạch mã hóa 4 sang 2 có bốn đầu vào Y3, Y2, Y1 & Y0 và hai đầu ra A1 & A0. Sơ đồ khối của mạch mã hóa 4 sang 2 như hình dưới.

Bạn đang đọc: Mạch mã hóa encoder là gì

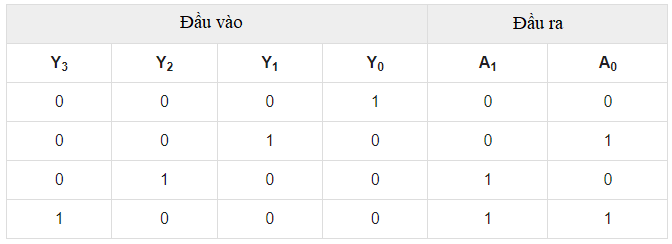

Tại bất kể thời gian nào, chỉ một trong 4 nguồn vào này hoàn toàn có thể là ‘ 1 ’ để nhận được mã nhị phân tương ứng ở đầu ra. Bảng chân trị của mạch mã hóa 4 sang 2 như bên dưới .

Từ bảng chân trị, tất cả chúng ta hoàn toàn có thể viết những hàm Boolean cho mỗi đầu ra như sau

A1 = Y3 + Y2

A0 = Y3 + Y1

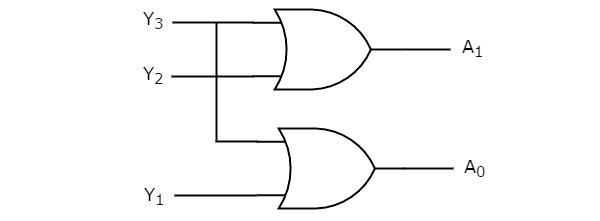

Chúng ta hoàn toàn có thể triển khai hai hàm Boolean trên bằng cách sử dụng hai cổng OR nguồn vào. Sơ đồ mạch mã hóa 4 sang 2 như hình dưới .

Sơ đồ mạch trên chứa hai cổng OR. Các cổng OR này mã hóa bốn đầu vào bằng hai bit .

Mạch mã hóa 8 sang 3

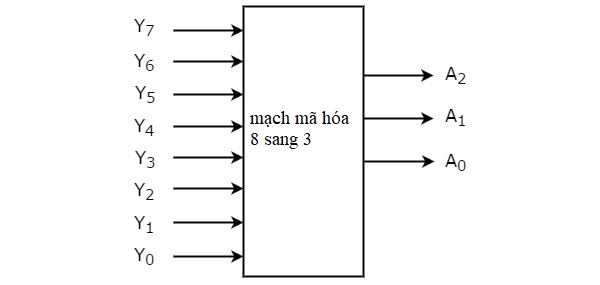

Mạch mã hóa 8 sang 3 có tám nguồn vào, Y7 đến Y0 và ba đầu ra A2, A1 và A0. Mạch mã hóa 8 sang 3 chính là mạch mã hóa bát phân sang nhị phân. Sơ đồ khối của mạch mã hóa 8 sang 3 như hình dưới .

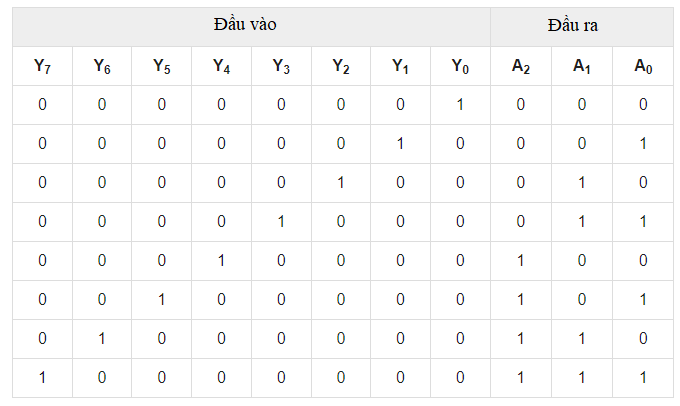

Tại bất kể thời gian nào, chỉ một trong tám nguồn vào này hoàn toàn có thể là ‘ 1 ’ để nhận mã nhị phân tương ứng. Bảng chân trị của mạch mã hóa 8 sang 3 như bên dưới .

Từ bảng chân trị, tất cả chúng ta hoàn toàn có thể viết những hàm Boolean cho mỗi đầu ra như sau

A2 = Y7 + Y6 + Y5 + Y4

A1 = Y7 + Y6 + Y3 + Y2

A0 = Y7 + Y5 + Y3 + Y1

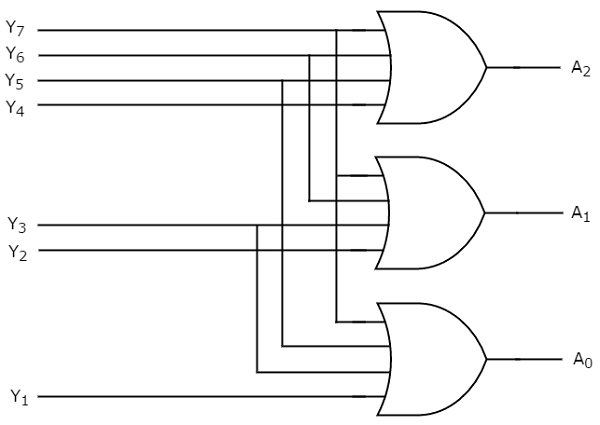

Chúng ta hoàn toàn có thể tiến hành những hàm Boolean ở trên bằng cách sử dụng bốn cổng OR nguồn vào. Sơ đồ mạch mã hóa 8 sang 3 như hình bên dưới .

Sơ đồ mạch trên chứa ba cổng OR 4 nguồn vào. Các cổng OR này mã hóa tám đầu vào bằng ba bit .

Hạn chế của mạch mã hóa

Sau đây là những hạn chế của mạch mã hóa thông thường.

Có một sự không rõ ràng, khi tổng thể những đầu ra của mạch mã hóa đều bằng không. Bởi vì, nó hoàn toàn có thể là mã tương ứng với những nguồn vào, khi chỉ có đầu vào ít quan trọng nhất là 1 hoặc khi tổng thể những đầu vào bằng 0 .

Nếu nhiều hơn một đầu vào đang hoạt động giải trí cao, thì bộ mã hóa tạo ra một đầu ra, hoàn toàn có thể không phải là mã đúng mực. Ví dụ : nếu cả Y3 và Y6 đều là ‘ 1 ’, thì bộ mã hóa tạo ra 111 ở đầu ra. Đây không phải là mã tương tự tương ứng với Y3, khi nó là ‘ 1 ’ cũng không phải là mã tương tự tương ứng với Y6, khi nó là ‘ 1 ’ .

Vì vậy, để khắc phục những khó khăn vất vả này, tất cả chúng ta nên phân quyền ưu tiên cho từng nguồn vào của mạch mã hóa. Sau đó, đầu ra của mạch mã hóa sẽ là mã nhị phân tương ứng với những nguồn vào Cao đang hoạt động giải trí, có mức ưu tiên cao hơn. Mạch mã hóa này được gọi là mạch mã hóa ưu tiên .

Mạch mã hóa ưu tiên

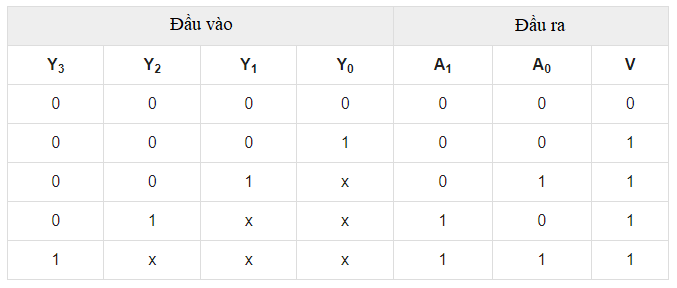

Mạch mã hóa ưu tiên 4 sang 2 có bốn đầu vào Y3, Y2, Y1 và Y0 và hai đầu ra A1 và A0. Ở đây, nguồn vào, Y3 có mức ưu tiên cao nhất, trong khi đầu vào, Y0 có mức ưu tiên thấp nhất. Trong trường hợp này, ngay cả khi nhiều hơn một nguồn vào là ‘ 1 ’ cùng một lúc, thì đầu ra sẽ là mã nhị phân tương ứng với nguồn vào, có mức độ ưu tiên cao hơn .

Chúng ta xem xét thêm một đầu ra nữa, V để biết mã có sẵn ở đầu ra có hợp lệ hay không .

Nếu tối thiểu một nguồn vào của mạch mã hóa là ” 1 “, thì mã có sẵn ở những đầu ra là mã hợp lệ. Trong trường hợp này, đầu ra, V sẽ bằng 1 .

Nếu toàn bộ những nguồn vào của mạch mã hóa là ‘ 0 ‘, thì mã có sẵn ở những đầu ra không phải là mã hợp lệ. Trong trường hợp này, đầu ra, V sẽ bằng 0 .

Bảng chân trị của mạch mã hóa ưu tiên 4 sang 2 như bên dưới .

Sử dụng 4 map K biến để nhận được những biểu thức đơn giản hóa cho mỗi đầu ra .

Các hàm Boolean được đơn giản hóa là

A1 = Y3 + Y2

A0 = Y3 + Y2 ′ Y1

Tương tự, tất cả chúng ta sẽ nhận được hàm Boolean của đầu ra, V là

V = Y3 + Y2 + Y1 + Y0

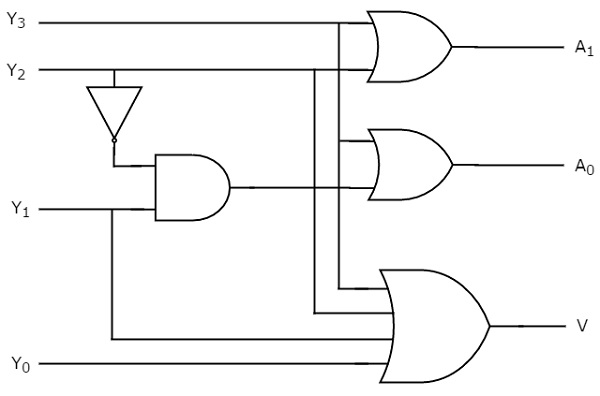

Chúng ta hoàn toàn có thể thực thi những hàm Boolean ở trên bằng cách sử dụng những cổng logic. Sơ đồ mạch mã hóa ưu tiên 4 sang 2 như hình bên dưới .

Sơ đồ mạch trên chứa hai cổng OR 2 nguồn vào, một cổng OR 4 nguồn vào, một cổng AND 2 đầu vào và một inverter. Ở đây, phối hợp cổng AND và inverter được sử dụng để tạo ra mã hợp lệ ở những đầu ra, ngay cả khi nhiều nguồn vào bằng ‘ 1 ’ tại cùng một thời gian. Do đó, mạch này mã hóa bốn đầu vào với hai bit dựa trên mức độ ưu tiên được gán cho mỗi nguồn vào .

Source: https://dvn.com.vn

Category: Cảm Nang